超大規(guī)模集成電路設(shè)計中的軟件開發(fā) 基本概念與核心角色

超大規(guī)模集成電路(VLSI)設(shè)計是一個極其復(fù)雜的過程,其實現(xiàn)不僅依賴于先進(jìn)的半導(dǎo)體工藝,更離不開一套強大、專業(yè)的軟件開發(fā)工具鏈。可以說,軟件開發(fā)是VLSI設(shè)計從抽象概念轉(zhuǎn)化為物理芯片的橋梁與引擎。本文將探討VLSI設(shè)計中軟件開發(fā)的基本概念及其核心組成部分。

VLSI設(shè)計中的軟件開發(fā)并非指設(shè)計某一款具體的應(yīng)用軟件,而是指用于輔助、實現(xiàn)和管理芯片設(shè)計全流程的專用軟件工具、平臺、語言和方法學(xué)。其核心目標(biāo)是提高設(shè)計效率、保證設(shè)計正確性、優(yōu)化芯片性能并控制成本與風(fēng)險。

一、電子設(shè)計自動化:軟件工具鏈的核心

電子設(shè)計自動化(EDA)是VLSI設(shè)計軟件開發(fā)的集中體現(xiàn)。EDA工具構(gòu)成了覆蓋芯片設(shè)計全生命周期的軟件生態(tài)系統(tǒng),主要包括:

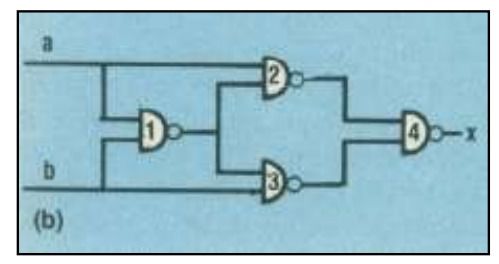

- 前端設(shè)計工具:涉及用硬件描述語言(如Verilog, VHDL)進(jìn)行電路建模、仿真驗證和邏輯綜合。這些工具將設(shè)計師的行為級或寄存器傳輸級描述,轉(zhuǎn)化為門級網(wǎng)表。

- 后端設(shè)計工具:負(fù)責(zé)將門級網(wǎng)表轉(zhuǎn)化為實際的物理版圖。包括布局(將電路單元放置到芯片平面上)、布線(連接各單元)、時鐘樹綜合、物理驗證(設(shè)計規(guī)則檢查DRC、版圖與電路圖一致性檢查LVS)等。

- 驗證與仿真平臺:這是確保芯片功能正確的關(guān)鍵。包括數(shù)字仿真器、形式驗證工具、硬件加速仿真以及近年來快速發(fā)展的硬件/軟件協(xié)同仿真與驗證平臺。

二、核心編程語言與腳本

VLSI設(shè)計軟件開發(fā)依賴于特定語言:

- 硬件描述語言:Verilog和VHDL是行業(yè)標(biāo)準(zhǔn),用于描述電路的結(jié)構(gòu)與行為。

- 腳本語言:Tcl因其與EDA工具深度綁定而成為設(shè)計流程自動化的“粘合劑”。Python憑借其強大的庫生態(tài)(如用于數(shù)據(jù)分析的Pandas, NumPy)和易用性,在流程自動化、數(shù)據(jù)處理和工具開發(fā)中扮演著越來越重要的角色。Perl也曾被廣泛使用。

- 專用建模與驗證語言:SystemVerilog(集成了設(shè)計、斷言和功能驗證特性)和UVM(通用驗證方法學(xué))庫是構(gòu)建復(fù)雜驗證環(huán)境的基礎(chǔ)。

三、設(shè)計方法學(xué)與流程管理

軟件開發(fā)也體現(xiàn)在高層次的設(shè)計方法學(xué)上,例如基于IP(知識產(chǎn)權(quán)核)的重用設(shè)計。這需要相應(yīng)的軟件平臺來管理龐大的IP庫,處理IP集成、驗證和交付。整個設(shè)計流程(從RTL到GDSII)的自動化管理與監(jiān)控,也依賴于定制開發(fā)的流程管理腳本和軟件,以確保各階段無縫銜接、數(shù)據(jù)一致。

四、算法與模型開發(fā)

在EDA工具背后,是大量復(fù)雜的算法,如邏輯優(yōu)化算法、布局布線算法、時序分析算法、功耗分析模型等。開發(fā)更高效、更精確的算法和數(shù)學(xué)模型,是推動VLSI設(shè)計技術(shù)進(jìn)步的關(guān)鍵軟件創(chuàng)新領(lǐng)域。

五、與制造和測試的接口

設(shè)計完成的軟件數(shù)據(jù)(最終版圖GDSII)需交付給晶圓廠。為此開發(fā)的軟件需要處理工藝設(shè)計套件(PDK)、設(shè)計規(guī)則文件,并生成測試芯片所需的測試向量。可測試性設(shè)計(DFT)工具也依賴于專門的軟件來實現(xiàn)自動插入掃描鏈、內(nèi)建自測試等結(jié)構(gòu)。

****

在超大規(guī)模集成電路設(shè)計中,軟件開發(fā)是貫穿始終的神經(jīng)系統(tǒng)和生產(chǎn)力基礎(chǔ)。它不僅僅是工具的使用,更涵蓋了從專用語言、算法創(chuàng)新、流程自動化到復(fù)雜系統(tǒng)管理的全方位工程實踐。隨著芯片復(fù)雜度持續(xù)攀升和先進(jìn)工藝的發(fā)展,對更智能、更集成、更高效的軟件開發(fā)需求將日益迫切,人工智能與機器學(xué)習(xí)在EDA領(lǐng)域的應(yīng)用正是這一趨勢的鮮明體現(xiàn)。掌握這些軟件開發(fā)的基本概念與技能,已成為現(xiàn)代VLSI工程師的必備素養(yǎng)。

如若轉(zhuǎn)載,請注明出處:http://www.myvrldk.cn/product/79.html

更新時間:2026-04-08 01:21:28